Fabric

The Gen-Z Consortium this week released Physical Layer Specification 1.1 for Gen-Z interconnects. The new standard adds enhanced support for PCIe Gen 5 as well as Gen-Z 50G Fabric and Local PHY. The publication of the new PHY revision enables chip developers to implement support for the technologies in upcoming devices featuring Gen-Z interconnects. Designed to offer high bandwidth and low latency for connections between processors, co-processors/accelerators, and memory/fast storage, Gen-Z 1.0 uses a PCIe physical layer and a modified IEEE 802.3 Ethernet electrical layer standards to provide per-lane speeds of up to the 56 GigaTransfers/second. The Gen-Z 1.0 physical layer specification only defined usage of PCIe Gen 1-4 protocols as well as a 25 GT/s PHY. Thus, to take advantage of all the capabilities...

Gen-Z Interconnect Core Specification 1.0 Published

The first major release of the Gen-Z systems interconnect specification is now available. The Gen-Z Consortium was publicly announced in late 2016 and has been developing the technology as...

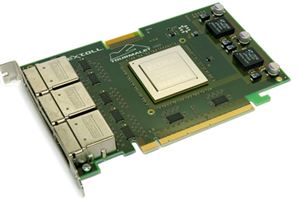

23 by Billy Tallis on 2/13/2018Host-Independent PCIe Compute: Where We're Going, We Don't Need Nodes

The typical view of a cluster or supercomputer that uses a GPU, an FPGA or a Xeon Phi type device is that each node in the system requires one...

8 by Ian Cutress on 12/21/2015